# Realization of a Diffraction-Based 1xN Optical Switch

Rachel Sampson

Dr. Pierre-Alexandre Blanche

August 4th, 2015

THE UNIVERSITY OF ARIZONA

College of

Optical Sciences

## Motivation

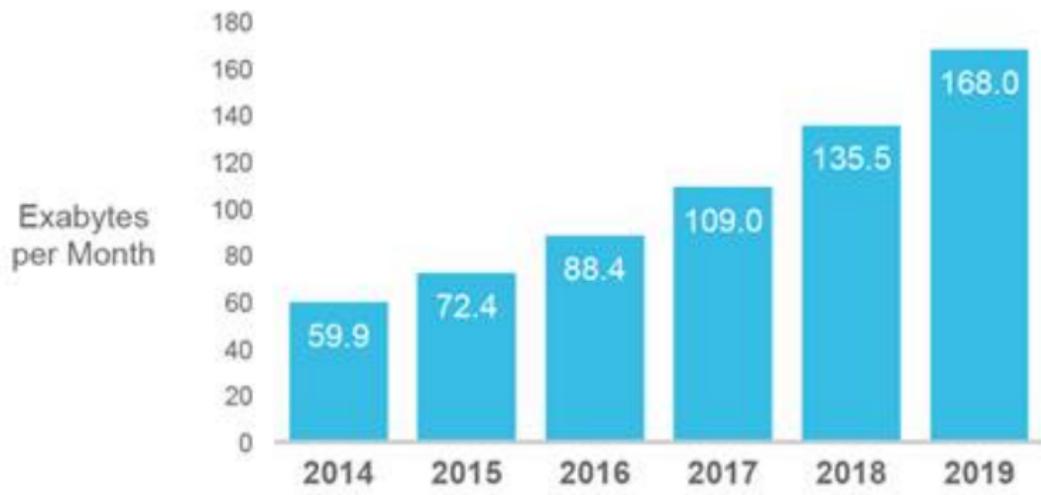

- ▶ Significant growth in data traffic

Figure 1: IP traffic per month forecasts <sup>1</sup>

---

<sup>1</sup>Image courtesy of Cisco Visual Network, Inc

## Background

- ▶ Information transmitted via optical fibers due to large bandwidth

- ▶ Switches: reroute information, connect fibers

- ▶ Historically, switches converted optical signal to electrical to optical

- ▶ Bandwidth bottleneck

- ▶ Slow

- ▶ Rigid

# Diffraction-Based Optical Switch

- ▶ Protocol- and bandwidth-invariant

- ▶ Rapid reconfiguration time

- ▶ Easily reconfigured

- ▶ Decouples send- and receive-side components → independent scaling of two sections

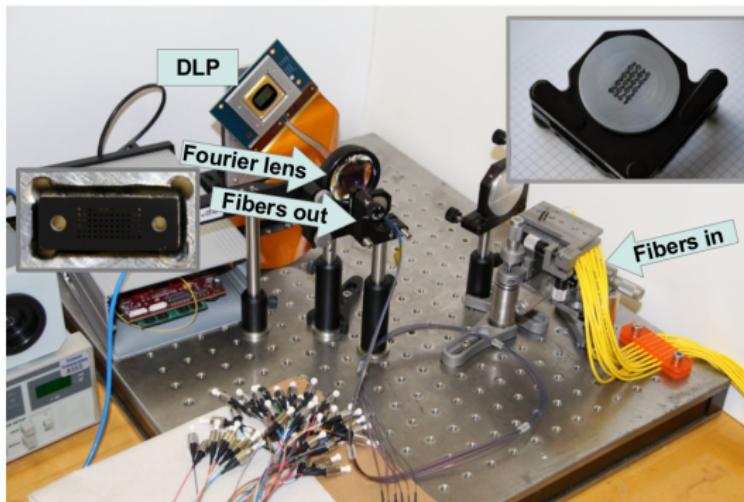

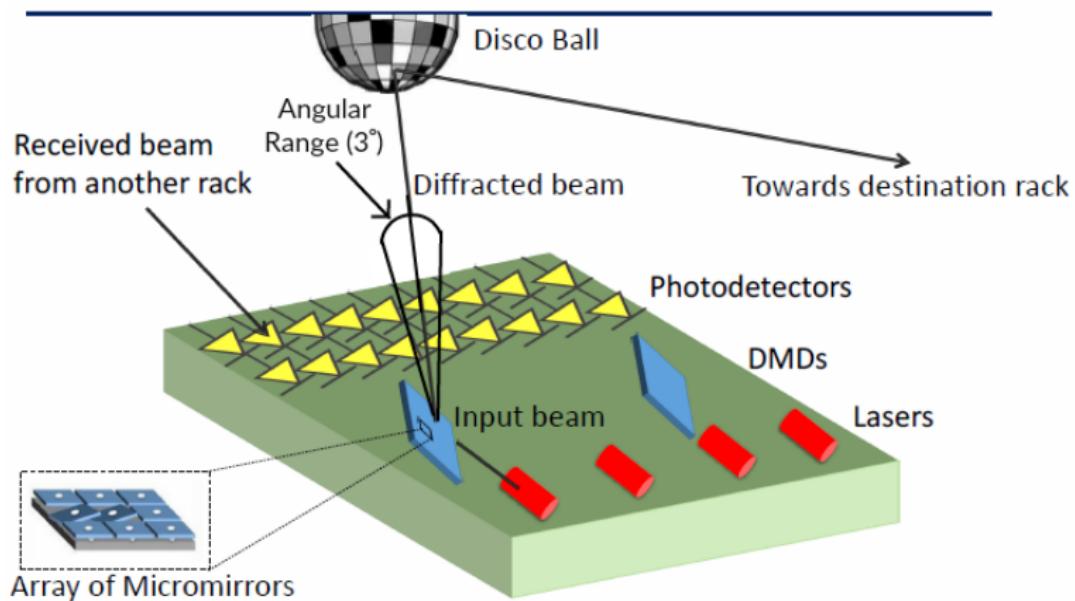

Figure 2: 32 x 32 diffraction-based optical switch

# Diffraction-Based Optical Switch

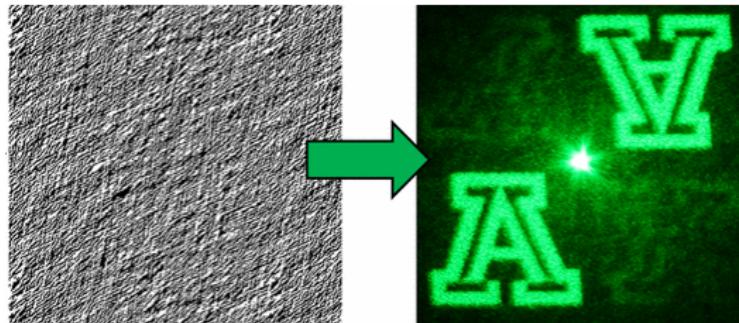

- ▶ Use computer generated holograms on DMD to diffract light

- ▶ Diffracts into precalculated pattern

Figure 3: Hologram and diffraction pattern produced when illuminated with laser light

Figure 4: DMD <sup>2</sup>

---

<sup>2</sup>Image courtesy of Texas Instruments

# 1xN Diffraction-Based Optical Switch

Figure 5: Top of rack within data center

# 1xN Diffraction-Based Optical Switch II

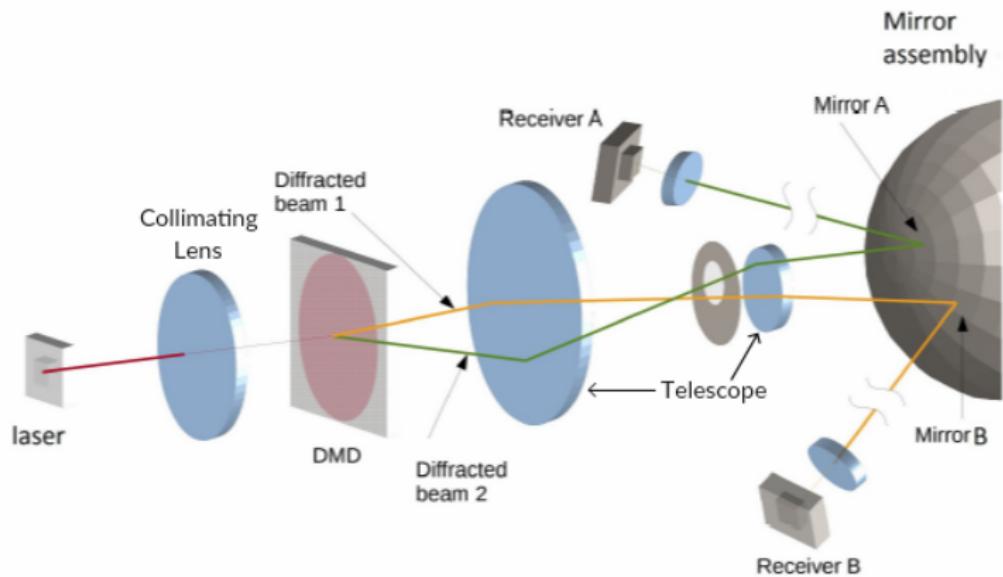

Figure 6: Schematic of 1xN optical switch

# Designing the Switch

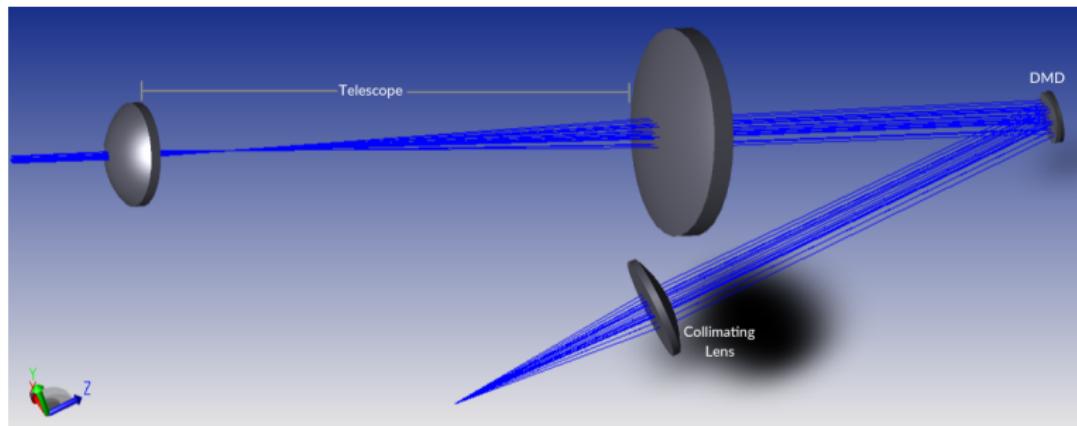

Figure 7: Schematic of 1xN optical switch

# Modeling the Switch

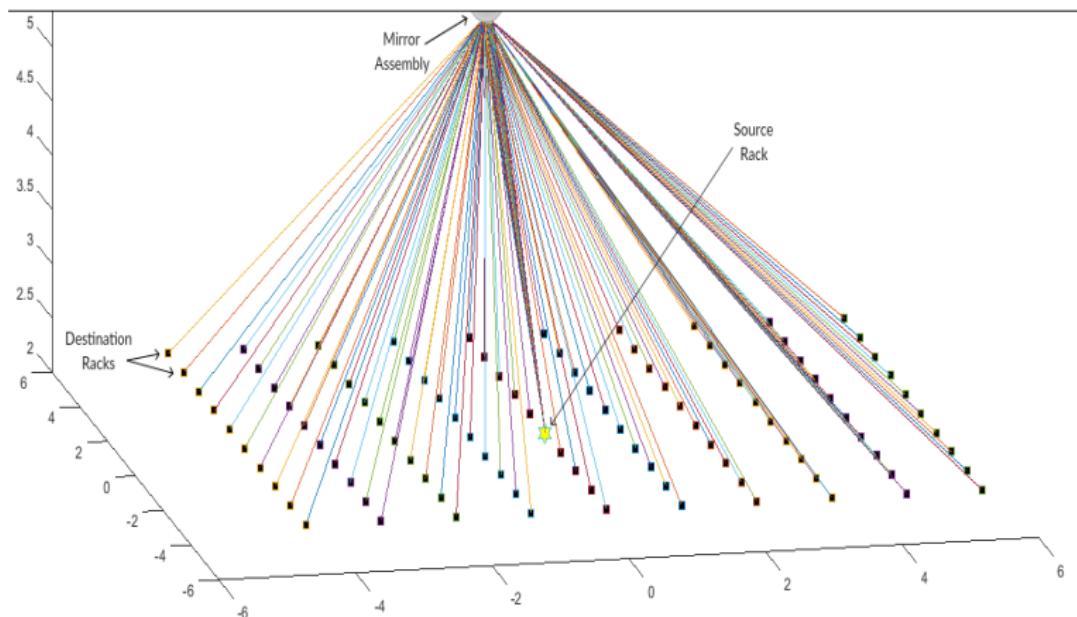

Figure 8: Ray tracing diagram from source rack to destination racks

# Number of Accessible Locations

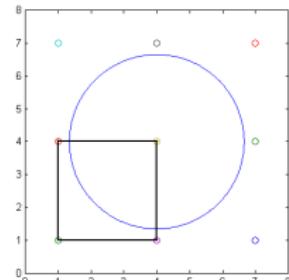

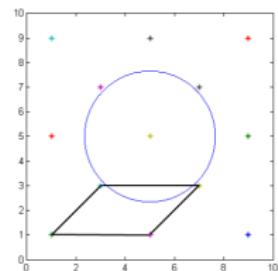

(a) Square

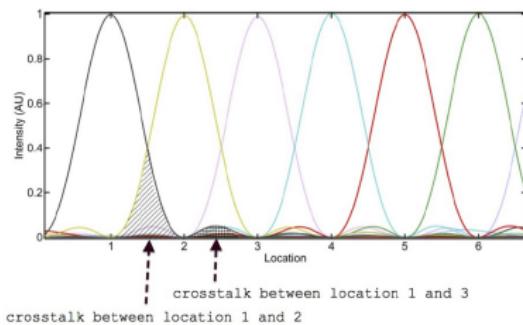

Figure 9: Adjacent beams diffracted from the DMD

- ▶ 12.5% increase in accessible locations

- ▶ 44 k vs. 50 k points

(b) Parallelogram

## Future Plans

- ▶ Design mirror assembly in Solidworks and machine

- ▶ Experimentally test design

- ▶ Increase number of output ports

## Acknowledgements

- ▶ Jilian Nguyen and Feibien Chen

- ▶ Alex Miles, Brittany Lynn, and Colton Bigler

- ▶ NSF grant #EEC-0812072 and #CHE-1156598

- ▶ University of Arizona Tech Launch Arizona POC Program

- ▶ Texas Instruments